# **MICRAL** USERS MANUAL

réalisations études électroniques zone d'activités de courtaboeuf avenue de scandinavie 91400 orsay 907 47 77

# HARDWARE

.

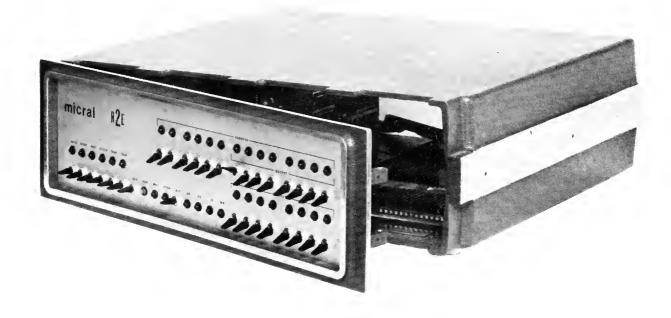

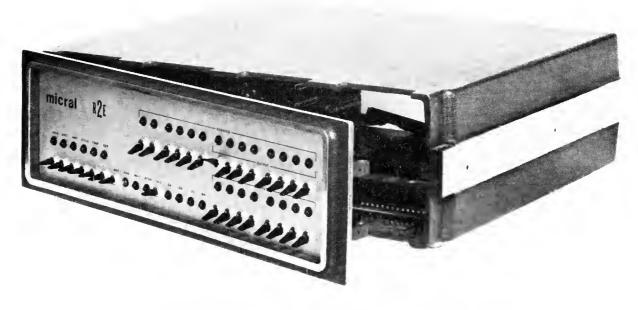

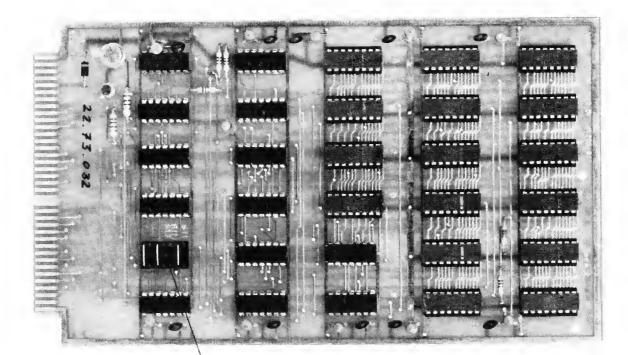

PHOTO 1

MICRAL with front control panel

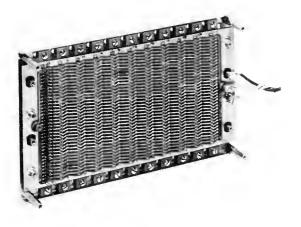

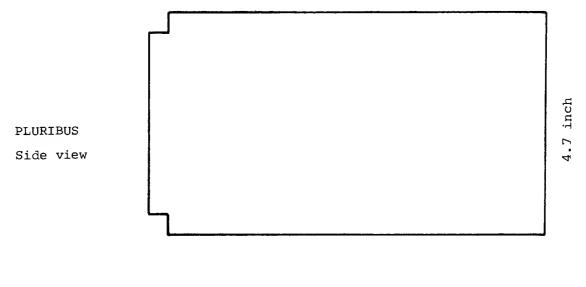

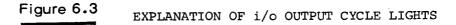

PHOTO 2 PLURIBUS

PHOTO 3 Inside view of the MICRAL with one Pluribus

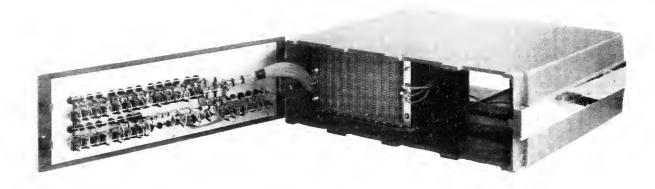

PHOTO 4 MICRAL with front panel open

PHOTO 1.1 Computer block with front pannel

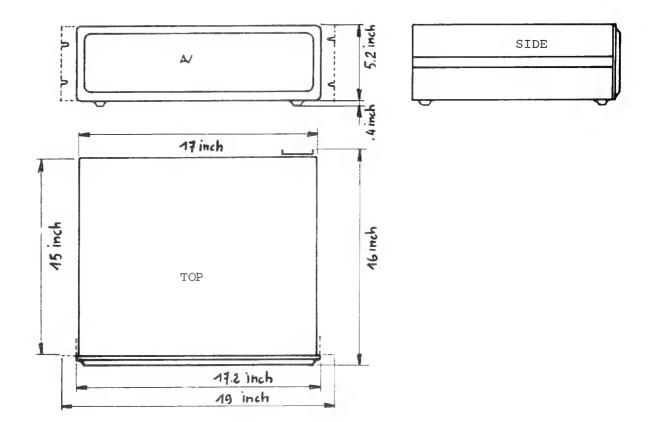

# Figure 1.1 Computer block size

#### I - GENERAL INFORMATION

I.l. Description

MICRAL has two parts :

- the computer block;

- the power supply block.

#### I.2. Computer block

The computer block consists of a cast of aluminium frame on which the pluribus is mounted. The latter has a printed circuit plugged into eleven identical 74-pin connectors through which the information is fed into and taken out of the pluribus. The connectors can accept any of the cards making up the MICRAL system at random.

In the standard version, one can load up to eleven cards on the pluribus. However, enough room is left on the frame to add on a second pluribus, thereby providing a maximum capacity of 22 standard cards.

The user can also replace the pluribus by a personalized bus to adapt his own Hardware. Note that all the power supply is oversized so to feed the necessary power to all the standard and special circuits. The outside connections are carried out at the end of the cards. The cards are built so as to prevent their being set upsidedown on the pluribus. Picture 1.1. shows the mechanical dimensions of the computer block. The computer block can be supplied in the rack form, upon request.

#### I.3. Power supply

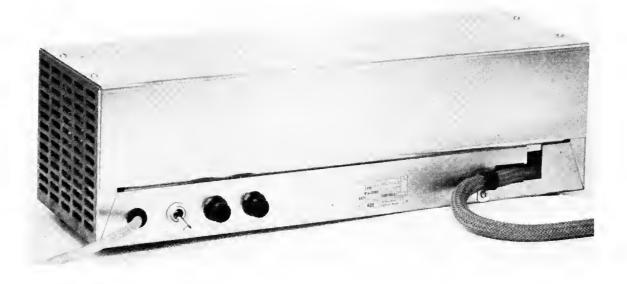

Picture 1.1 shows MICRAL fitted with both its power supply and computer block. The two blocks are connected in the basic configuration by a 2,5 meters long cable. The main supply cable is 2 m long.

The power supply block includes the start switch as well as two fuses to protect the equipment (one for each phase). The main supply consumption, for the standard configuration, is less than 250 W. One must use a D1 TD 2 type, 2 A delay fuse. The power supply block feeds the installation with the following regulated voltages :

> $5 V \pm 1\%$  at 10 A. -  $9 V \pm 1\%$  at 4 A.

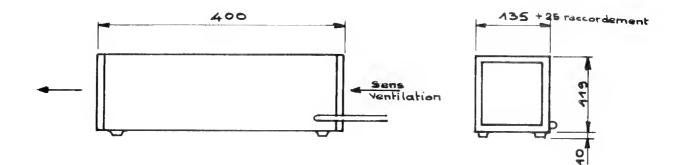

Picture 1.2 shows the mechanical dimensions of the power supply unit.

РНОТО 5

POWER SUPPLY

FIGURE 1.2 DIMENSIONS

Consumption : 250 W

Sing  $\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$  connector card

Double connector card

#### I.4. Construction

One the fundamental features of MICRAL is its ability to provide memory capacity and the number of interfaces strictly necessary to solve a particular problem. The construction of the computer is therefore highly modular.

Picture 1.4 shows one card and its dimensions.

For example, the Random Access Memory can be made of cards containing each a maximum of 2 K bytes. When more than 2 K is required, the system will have to be equipped with more than one RAM card. All RAMS being identical, the user will have to assign them an address so to enable the processor to address them correctly.

The following paragraph explains how the address assignment system works in MICRAL.

#### I.5. Address assignment

Generally speaking, each card has several cards (memories or interfaces). Decoders allow one to select the addressed card among the total of cards included on the card. A selector circuit allows one to select the card when the addressed card is included in that card.

The address of the card is taken from SO/ to S13/ pluribus Terminals, the low order bits address the card on the card and the high order bits the card in the system.

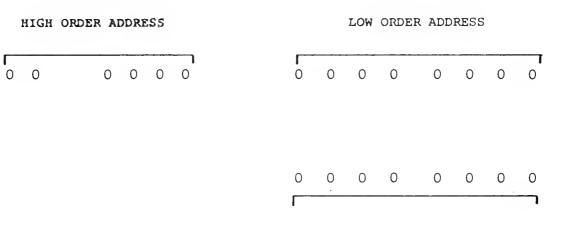

#### I.5.1. Memory addresses assignment

The fourteen bits of the address register allow one to address 16 K bytes as follows :

SO/TO S7/ address the byte on the page; S8/to S10/ (in 2 K RAM card) or S8/to S11/ (in 4 K RAM card) address the page in the card and S11/to S13/ or S12/to S13/ address the card in the system.

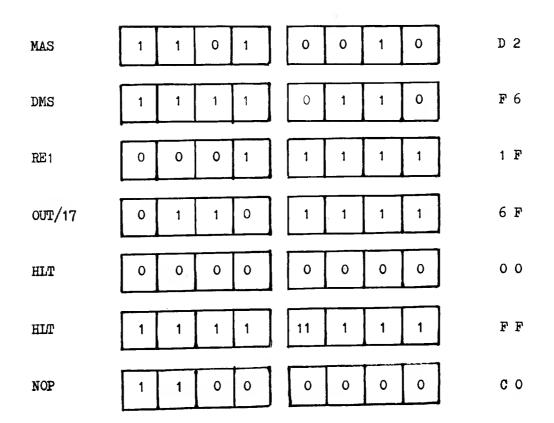

The selector circuit works on the latter bits. On each bit number "i", it is possible to feed Si or Si/ depending on whether a "1" or "O" is to be assigned to this bit. This is done with an integrated circuit support on which are connected, on one side, facing each other, one input of the selector and circuit and, on the other, Si and Si/ signals. A jumper allows the user to connect the Si to the input when a "1" is to be assigned or the Si/ when a zero is to be assigned.

Example : place the jumper to assign a 2 K RAM card in a such way that page 1F is included. F will address the seventh page of the card and "1" will address the card in the system. The binary address being OO1, S13/, S12/ and S11 should be connected to the selector inputs and the jumper placed as shown on figure 1-5. I.5.2. Coupler cards

S9/ to S13/ address the output devices and SO/ to S7/ the input devices while S9/ to S11/ address the group of input devices.

The description of coupler address assignment is described in the corresponding paragraph.

.

#### II - PROCESSOR CARD M1100

#### II.1. Hardware description

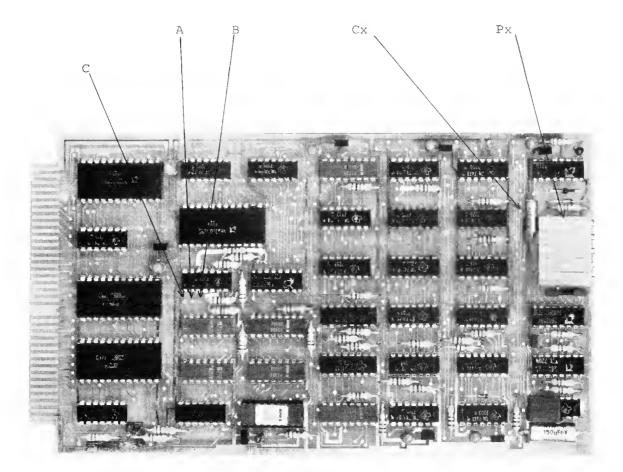

Photograph 2.1. shows the processing card.

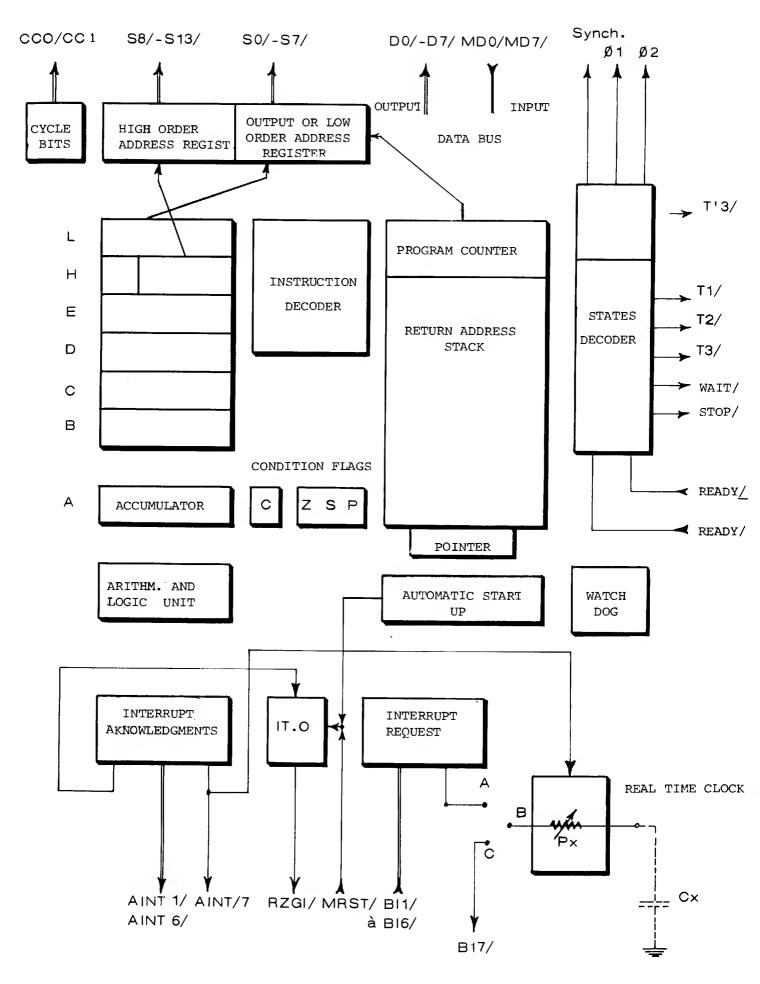

It has a micro-processor 8008 and its associated circuits allowing the decoding of the machine states and synchronization. Also included in the processor is the interrupt system, a real time clock, the automatic start-up circuits and the general address register of fourteen bits permitting the direct address of to 16 K memory words and the control of the I/O, as well as a control light diode. Diagram 2.2 shows schematically the card's layout.

#### II.1.1. Registers

The processor contains seven registers addressable by the internal instructions :

| Α    | the accumulator                                          |

|------|----------------------------------------------------------|

| BCDE | auxiliary registers                                      |

| H L  | auxiliary registers allowing to address the main memory. |

These seven registers have an internal address which is respectively 0 - 1 - 2 - 3 - 4 - 5 - 6. Address 7 relates to the memory M addressed by registers H and L. H relates to the higher order bits of the address (six bits) and L to the lower order bits of the address (eight bits).

#### II.1.2. The program counter

The program counter is located in a push-down stack consisting of a Random Access Memory of eight registers of 14 bits addressed by a pointer. This pointer is decreased by each sub-routine call instruction (CAL or RST).

The new program counter (which is the address of the required subprogram) is recorded in the memory at the address determined by the pointer. The former program counter (i.e. the return address) is memorized in the address below, in the stack.

When a return instruction is decoded by the processor, the pointer is incremented. The program is then connected to the return address. This system permits the overlapping of up to seven sub-routines without losing the return address of the main program.

#### II.1.3.Condition Flags

Four flags are simultaneously set to each operation.

FIG. II.1 - PROCESSOR BLOCK DIAGRAM

11

- Carry : this flag is set to "1" when there is an under or overflow on the accumulator. It is set to zero by logical operations. It is not affected by load instructions or by increment or by decrement of the registers (B.C.D.E.H.L.).

- Zero : this flag is set to "1" when the result of an operation is zero.

- Sign : this flag is set to "1" when an operation leads to a result where the highest order bit is "1". The term "sign" has been kept, although it is incorrect, analogically with the 2's complement code in which the highest order bit is the sign.

- Parity: the flag is set to "1" when the result of an operation gives a result where the bits count is even.

In order to avoid any ambiguity, diagram 2.1. shows the state of flags C Z and S after a substraction or comparison instruction for the various cases : accumulator lower, equal or superior to the ground.

Picture 2.1. Position of flag after one operation SUr or CPr.

In the event the user wants the 2'S complement code, this diagram does not apply.

The conditional call or jump instructions allow these flags to be tested and to connect the program according to these states.

#### II.1.4. Interrupt system

Each interrupt level relates to one input, except level zero (called "catastrophic"), which is always active, each level can be enabled or disenabled individually, masked or unmasked collectively.

When an interrupt is activated, the program is connected to one of the eight adresses of page O:

/0 - /8 - /10 - /18 - /20 - /28 - /30 - /38

(Addresses are specified in hexadecimal when preceded by a/).

Each address is the beginning of a sub-program including up to eight sequencial instructions (to avoid overflowing into an higher level address). The first instruction of each of these sub-programs is not interruptible. Level 7 can be connected to the real time clock (connect A to B). The interrupt system includes also eight acknowledgement outputs.

## II.1.5. The real time clock

The real time clock can be adjusted from 100 micro-seconds to one hour, with infinite variation. In the standard configuration, the internal clock is supplied with a 10 m.sec. period. The roughing out is done with the CX capacitor which must be adjusted to the desired duration scale. Fine adjustment is made with a PX potentiometer.

#### II.1.6. Synchronisation signals

#### II.1.6.1. PRINCIPLE

Knowledge of the synchronization system is not a must for the user. As a matter of fact, MICRAL operates under the following principle : at each addressing phase (for a fetch cycle, as well as for exchange of data between processor and memories, or processor and peripherals), the processor stops in a WAIT state, until the addressed device has sent a low voltage signal back to READY input of the pluribus which sets the processor back to active working, in synchronization with the time base. The WAIT state has a duration which is a multiple of the clock period. If READY comes early enough, the WAIT state is skipped. To obtain this result, the low voltage signal must be sent back to READY input at the latest 500 nanoseconds after the higher part of the address has been received from the processor on the pluribus.

When the processor is in the WAIT state, this is signified by a low voltage signal to the pluribus'WAIT/output. The WAIT cycle is used to obtain a "step" through the console. The console sends back a low voltage signal to READY input which systematically holds the processor in a WAIT state until an high level voltage (5 V) has been sent back by means of the step by step key on the console (see console description).

- II.1.6.2. The time base has two phases which are used as a reference. The processor returns a synchronisation voltage of half the SYNC period. SYNC/ period is the basic period for the machine (4 micro-seconds). The instruction is divided into memory cycles, themselves divided into machine states.

- II.1.6.3. Memory cycles : there are four types of memory cycles (OP, READ, WRITE, I/O) which are defined by the state of the two CCO and CC1 outputs as shown on diagram 2.2.

Fetch cycle

This cycle corresponds to the addressing of the memory during the fetch phase.

|     | A r | A = r | A r |

|-----|-----|-------|-----|

| C · | 1   | 0     | 0   |

| Z   | 0   | 1     | 0   |

| S   | 1   | 0     | 0   |

| Figure 2.1 | Position c | of flag | after one |

|------------|------------|---------|-----------|

|            | operation  | SUr or  | CPr       |

| Cycle | CC 0 | CC 1 |

|-------|------|------|

| OP    | 0    | 0    |

| LEC   | 0    | 1    |

| ECR   | 1    | 1    |

| E/S   | 1    | 0    |

|       |      |      |

Figure 2.2 Memory cycles coding

This cycle relates to the addressing of the memory when reading data.

WRITE Cycle

It is in operation when the program requires writing of data into the memory.

I/O Cycle

This cycle refers to an exchange of data between the processor and an input or output. It includes an addressing phase of the peripheral and an exchange phase.

#### II.1.6.4. <u>Machine states</u>: cycles are composed of states, being multiples of the basic period.

Five states last for one basic period (T1, T2, T3, T4, T5) and two states have a duration depending on the system. One of them is the WAIT state mentioned above, the other is the STOP state.

- States of fixed duration :

- . T1 Addressing of the lower order part of the address.

- . T2 Addressing of its higher order part.

- . T3 Instruction decoding.

- . T4 Instruction execution.

- **.** T5

- States of indefinite duration :

- . WAIT state described above.

- STOP : the computer is in an idle state necessitating restarting by means of an interrupt.

#### II.1.7. Automatic start

The automatic start system consists of detecting the raise of the power supply voltages and generating a zero level interrupt (INIT), which connects the program back to zero address. A restart is also obtained by generating zero level interrupt. The same result can be obtained by depressing the INIT key from the console.

## II.1.8. Optical "watch-dog" signal

As just indicated, zero level interrupt cannot be disenabled. Now, bit O of OUTPUT /17 which is not used to activate the interrupt level zero, controls a flag connected to a light emitting diode which acts as an optical "watch-dog" signal. State "1" of the flag relates to the light being extinguished.

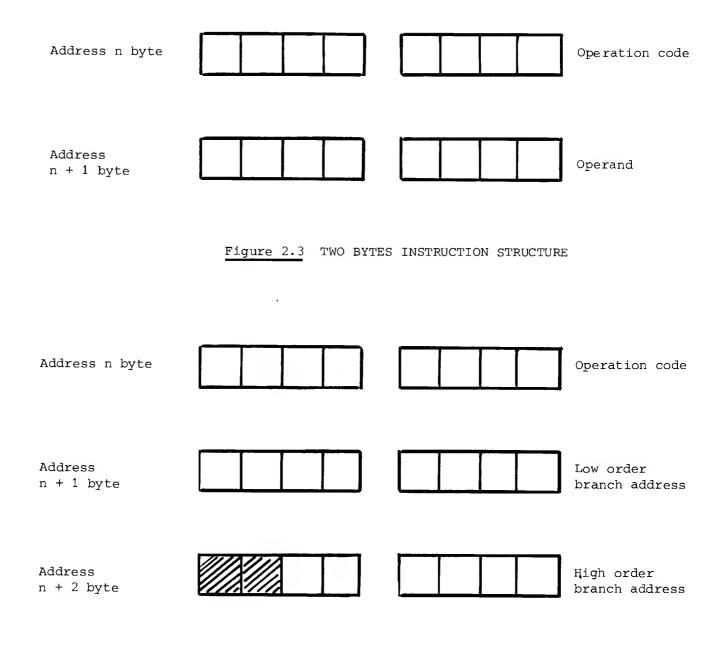

Figure 2.4. THREE BYTES INSTRUCTION STRUCTURE

Incidentally, this device is used for the 1, 2, 3, 4 maintenance program of the MICRAL library. In order to check MICRAL functionnally, load this program and ensure that the diode lights up according to program.

#### II.2. Description of instructions

#### II.2.1. Structure of instructions

MICRAL instructions are generally contained in a byte. Some instructions are contained in two bytes. These instructions use as an argument data located in the byte immediately following the operation code (see diagram 2.3).

On the other hand (see diagram 2.4) connecting instructions (jumps or calls) are contained in three bytes, the first containing the operation code, the second the lower order address (eight bits), the third the page address (six bits, the two heaviest bits being inoperative).

Instructions can be divided into several groups:

- . loadings.

- . arithmetical and logical operations.

- . connections.

- . input output.

- . machine instructions.

These are also pseudo-instructions of the assembler that will be examined in chapter relating to the software.

In the following paragraphs, instructions are described group by group.

#### II.2.2. Loading instructions

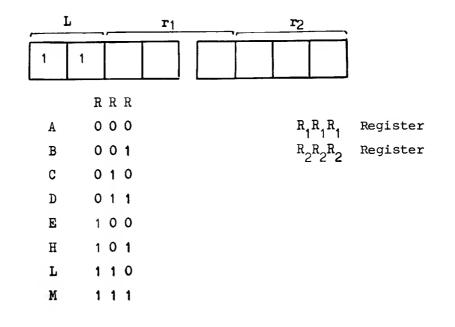

- II.2.2.1. General structure : in these instructions, each register is designated by its internal code (A=O, B=1, C=2, D=3, E=4, H=5, L=6). In memory reference instructions, the address shown by H and L, called M, is designated by code 7. Simple loading instructions are contained in one byte, while immediate loading instructions are contained in two bytes.

- II.2.2.2. Simple loading instructions :

The commonest form of simple loading is :

Lr<sub>1</sub>r<sub>2</sub>

It means load  $r_1$  with the content of  $r_2$  (the latter remaining unchanged with :

$$r_1 = A, B, C, D, E, H, L, M'$$

$r_2 = A B C D E H L M$

As can be seen, this instruction includes to operation code, bits, (the heaviest ones), and two zones of three bits which are internal addresses of the micro-processor (see diagrams 2.5 and 2.6).

Except LAA which is called NOP, Lrr type operations cannot be used as they perform operations such as masking and unmasking (see paragraph "machine instructions").

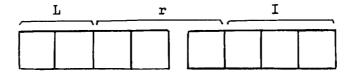

#### II.2.2.3. Immediate loading instructions :

The most general form of immediate loading instructions is :

It means load register r with the content of argument ARG placed in the byte immediately following the instruction (see diagrams 2.7 and 2.8).

Diagram 2.8 demonstrates how the accumulator can be cleared by means of instruction LAI O. We shall see later that another shorter instruction exists (XRA) enabling to clear the accumulator but with the inconvenience of modifying the flags.

#### II.2.3. Arithmetical and logical operations

These affect the flag on all operations, they divide into three categories :

- a) increment or decrement of auxiliary registers;

- b) arithmetical and logical operations on the accumulator;

- c) rotations of the accumulator.

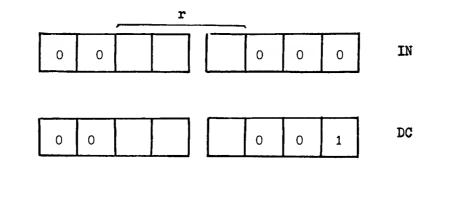

- II.2.3.1. Increment decrement (diagrams 2.9 and 2.10) = the most general

form of increment decrement instructions, is as follows :

```

IN r

```

#### DC r

#### $\mathbf{r} = \mathbf{B} \mathbf{C} \mathbf{D} \mathbf{E} \mathbf{H} \mathbf{or} \mathbf{L}$

They mean : increment (IN) or decrement (DC) the register r by one, and set Z,S and P flag according to the result, C remaining unchanged.

Figure 2.5 - SIMPLE LOADING INSTRUCTION STRUCTURE

| LAB | LOAD "A" WITH CONTENTS OF B              |

|-----|------------------------------------------|

| LCM | CHARGE "C" WITH MEMORY                   |

|     | INDICATED BY H + L                       |

| LME | WRITE IN THE MEMORY INDICATED BY H AND L |

|     | THE CONTENTS OF E                        |

.

Figure 2.6 - STRAIGHT FORWARD LOADING EXAMPLES

# Figure 2.7 - IMMEDIATE LOADING INSTRUCTION STRUCTURE

LAI 0 RESET THE ACCUMULATOR AT ZERO

.

LMI 0 RESET THE MEMORY INDICATED BY H AND L LLI1

LMI 0RESET THE MEMORY INDICATED BY H AND LLLI ADRBLOAD THE LOW ADDRESS MEMORY ADRBLHI ADRHAND HIGH ADDRESS ADRH

#### Figure 2.8 - EXAMPLES OF IMMEDIATE LOADING

Figure 2.9 - INCREMENT AND DECREMENT INSTRUCTION STRUCTURE

# LLI 0 FOLLOWING THESE INSTRUCTIONS L CONTAINS 1, INL CARRY IS UNAFFECTED Z, S AND P ARE FALSE

•

# Figure 2.10 - INCREMENT INSTRUCTION EXAMPLES

| 1    | 0    |   | OI | 2 | r = A, B, C, D, E, H, L ou M          |

|------|------|---|----|---|---------------------------------------|

|      |      |   |    |   |                                       |

| OP : | AD   | 0 | 0  | 0 | ADD A and r                           |

|      | AC   | 0 | 0  | 1 | ADD A, r and C (Carry)                |

|      | SU   | 0 | 1  | 0 | Subtract r from A                     |

|      | SB   | 0 | 1  | 1 | Subtract r + C (Carry) from A         |

|      | * ND | 1 | 0  | 0 | And Logic between A and r             |

|      | * XR | 1 | 0  | 1 | Or exclusive between A and r          |

|      | * OR | 1 | 1  | 0 | Or inclusive between A and r          |

|      | CP   | 1 | 1  | 1 | Compare : Set the flags in accordance |

|      |      |   |    |   | of the difference A - r without       |

|      |      |   |    |   | modifiing accumulator.                |

|      |      |   |    |   |                                       |

| Figure 2.11 | STRAIGHT F | ORWARD | OPERATION | INSTRUCTION | STRUCTURE |

|-------------|------------|--------|-----------|-------------|-----------|

|             |            |        |           |             |           |

,

| LAM | THIS PROGRAM ALLOWS TWO NUMBERS TO BE      |

|-----|--------------------------------------------|

| ADB | ADDED IN DOUBLE PRECISION ONE LAYS BETWEEN |

| LMA | TWO CONSECUTIVE MEMORY CASES THE           |

| INL | OTHER BETWEEN THE REGISTER B AND C         |

| LAM |                                            |

| ACC |                                            |

| LMA |                                            |

Figure 2.12 EXAMPLE SHOWING AN OPERATION

It is important to note that these instructions do not allow the modification of A or  $M_{\bullet}$

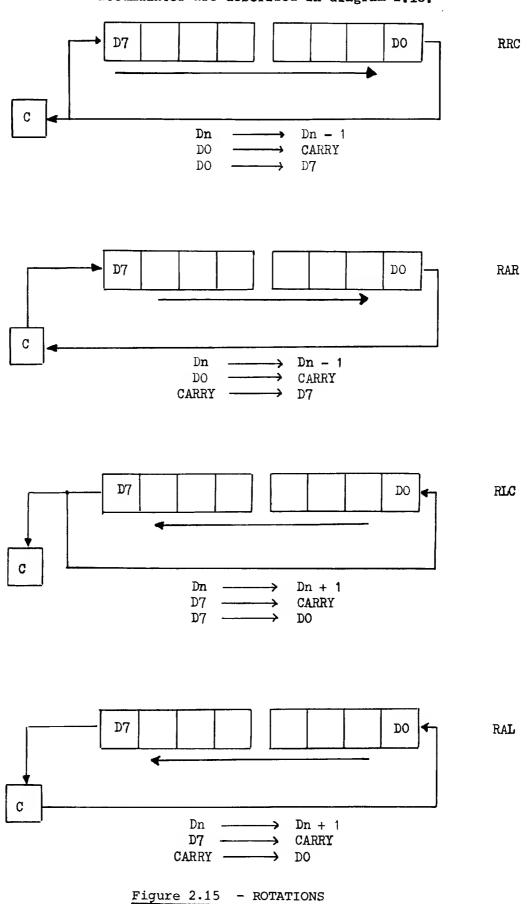

II.2.3.2. Simple arithmetical operations (diagrams 2.11 and 2.12): these instructions use two operands. One is contained in the accumulator, the other is designated by the instruction of either one of the registers A or M. The result is stored in A and all the controls are amended as a result.

> To demonstrate the instruction form, we use an auxiliary symbol OP (not recognized by the assembler) as representing one of the eight operation codes, accepted by the processor.

The OPr form means : perform operation OP between A and r, the result is stored in A.

The eight of codes are :

- AD for addition A and r;

- AC for addition A, r and C (Carry);

- SU for substraction r from A;

- SB for substraction r + C (Carry) from A;

- ND for and LOGICAL BETWEEN A and r;

- XR for or exclusive between A and r;

- OR for INCLUSIVE BETWEEN A and r;

- CP compare A and r and set the controls by the result of A-r without modifying A or r.

Note that in the example shown in diagram 2.12, the use of INL does not affect the condition of the carry flag thereby permitting the transfer of the instruction AC. In these operations, all flags are set by the operation's result. Where logical operations are concerned (as marked with an asterisk), the carry control is reset to zero.

II.2.3.3. Immediate operations : the usual form, OPI ARG, means : perform operation OP between the content of the accumulator and the argument contained in the memory byte immediately following the operation code of the instruction. The controls are set as per previous paragraph (see diagrams 2.13 and 2.14).

Figure 2.13 - FIRST BYTE OF AN IMMEDIATE

OPERATION STRUCTURE

NDI OFMASKS THE FOUR HIGHEST ORDER BITSADACLEARS ACCUMULATOR AND SETS FLAGS ON 0XRASETS FLAGS IN ACCORDANCE WITH CONTENT OF A.

CPA

Figure 2.14 - EXAMPLES OF OPERATIONS

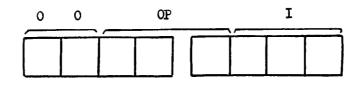

II.2.3.4. Accumulator's rotations : the rotation operations of the accumulator are described in diagram 2.15.

Figure 2.18 - RST INSTRUCTION EXAMPLE

rst 4 CALLS SUBROUTINE LOCATED AT ADDRESS /18

в

Figure 2.17 - EXAMPLES OF CONDITIONAL CONNECTIONS

JUMP TO ADDRESS IF THE CARRY IS JFC ARR IN A FALSE POSITION ("0" LOGIC) RETURN TO THE MAIN PROGRAMM IF THE RTZ ZERO ES IN THE TRUE POSITION

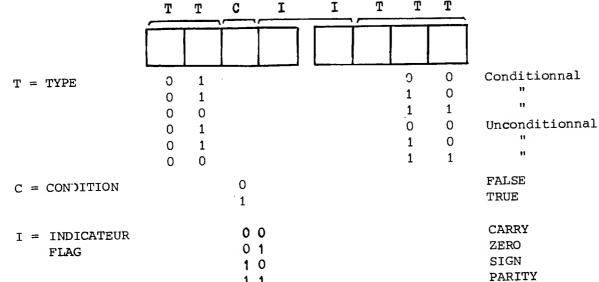

Figure 2.16 - BRANCH INSTRUCTION STRUCTURE

WHEN CONNECTED, UNCONDITIONALLY THE CII BITS ARE THE SAME EXCEPT FOR RET FOR WHICH THE 011 CONFIGURATION CANNOT BE USED IT GIVES REI.

Т

Т

Т

Ι

| INDICATEUR | 0 0 | CARRY  |

|------------|-----|--------|

| FLAG       | 0 1 | ZERO   |

| r lag      | 1 0 | SIGN   |

|            | 1 1 | PARITY |

|            |     |        |

|            |     |        |

C

Ι

#### II.2.4. Connection instructions

II.2.4.1. <u>Unconditional connections</u> : there are three types of unconditional connections :

JMP - CAL - RET

- JMP connects the program unconditionally to the address contained in the two bytes immediately following the OP code. The first byte contains the eight bits of the lower order address and the second byte the six bits of the page address. The code for the first byte is OIXXXIOO (X being either 1 or O).

- CAL has the same effect, but it memorizes the address of the program counter in the micro-processor's stack. This instruction allows calling of a sub-program. The code for the first byte is OIXXXIIO.

- RET connects the program to the first address memorized in the stack. This instruction is used to return from a sub-program. The code is OOXXXIII (X being immaterial except configuration OII).

- II.2.4.2. <u>Conditional connections</u> : there are three instructions in this category.

The first letter of the mnemonic instruction defines the type of operation (J for JMP, C for CAL, R for RET), the second letter defines the condition, T (True) or F (False) depending on whether the connection is desired upon the true or false condition, and the third letter specifies which control is to be tested to make the connection. Diagram 2.16 shows the structure of the connection instructions and diagram 2.17 two examples of conditional connections.

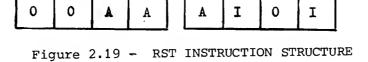

II.2.4.3. RST (CAL included in one byte) : there is another unconditional connection instruction which permits, in one single byte, the program to connect with one of eight addresses on the zero page.

This instruction is written : RST N, N being an argument ranging from 0 to 7, the program is connected to address  $8 N_{\bullet}$

See example (diagram 2.18) and structure (diagram 2.19). This instruction in spite of its form, is contained in one single byte. The argument is inserted into the instruction's code.

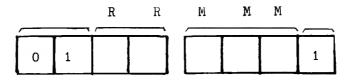

RRMMM is the device address, RR must be different to 00

Figure 2.20 - OUTPUT INSTRUCTION STRUCTURE

MMM is the group device ADDR

Figure 2.21 - INPUT INSTRUCTION STRUCTURE

.

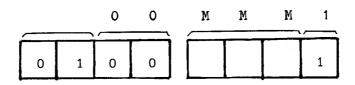

Figure 2.22 - MACHINE INSTRUCTION CODES

#### II.2.5. Input/output instructions

II.2.5.1. Outputs : there are 23 output instructions. They are in the OUT DEV form.

DEV is an argument inserted into the operation code representing the address of a card and necessarily ranging from O to 22 decimals (equivalent to O and /17 hexadecimal). The 23rd address is used to enable interrupt (paragraph II.26.4.).

Instruction RST (and instruction INP described below), also instruction OUT, in spite of its form, are located in one single byte of memory. Five bits are reserved for the argument, within the operation code.

II.2.5.2. Inputs : except when addressing a channel (see paragraph V), the input operation takes place in two steps. First, A, is precharged by an immediate loading instruction, then, instruction INP GRP is utilized. GRP is an argument inserted into the operation code representing the address of a group of inputs, ranging from 0 to 7. Each group includes 255 byte inputs, addressed by precharging A. It is possible to address 7 x 256, i.e. 1792 input bytes, equal to 14.336 single wire inputs.

Example :

LAI 12 gives input 12 of group 2.

Channels are called by their group address and thereby neutralize the 256 inputs corresponding to their group address.

- II.2.6. Machine instructions

- II.2.6.1. Instructions MAS : instruction MAS allows masking of the interrupts, i.e. it disengages all interrupt levels, except level 0.

- II.2.6.2. Instructions DMS : instruction DMS activates all the enabled interrupt levels, making them all operational. Immediately after instruction DMS has been executed, the program can be interrupted by the level of interrupt that holds the highest priority.

- II.2.6.3. <u>Return instruction RE1</u>: this instruction permits the performance of two operations simultaneously: one unconditional RET and one DMS. It avoids losing a level interrupt in certain instances ( a regular interruption between DMS and RET without RE1).

II.2.6.4. Enabling/Disenabling :

This instruction is an output instruction on address /17. It performs two functions :

- 1°) applying a signal to the optical "watch-dog" through bit 0:

- 2°) arming the interrupt levels in accordance with the configuration contained in the accumulator.

- A level of priority corresponds to each bit :

Bit 0 Watch-dog Bit 1 Level 1

Bit 7 Level 7

one "O" disenables the corresponding level.

One "1" re-enables it.

Example : LA1 04

OUT/17

Applies 0 to the watch-dog and disarms all levels except level 2.

LA1 OF applies A to the watch-dog and activates levels 1, 2 and 3.

II.2.6.5. Instructions HLT : renders the processor into a STOP condition.

Instruction NOP : it is inoperative.

.

Figure 2.23 OUTSIDE PROCESSOR CIRCUITS

#### II.3. Functioning of the Processor Board

#### II.3.1. Introduction

The general system, based on the request/acknowledgement principle, allows the user to ignore the functioning of the machine states.

When an interface card is addressed, it sends a low voltage signal to the READY/Terminal indicating that it is ready to supply or to collect the requested information.

If this signal does not arrive before T'3, the processor enters a wait state. Following the circumstances, the supplied information is accepted by the processor in the T'3 state which follows immediately upon addressing or after one or several WAIT cycles.

The processor then executes the instruction either in the current cycle, either in a new memory cycle.

A more detailed description is provided in the appendix 2 and 3 (example related to CFC instruction).

#### II.3.2. Interrupts :

II.3.2.1. Principle : MICRAL interrupt system is graded in eight levels, Level zero, designated by INIT, called catastrophic, cannot be masked nor disenabled. The others can be masked and unmasked as a whole, and individually enabled or disenabled by meansof an internal mask generated by an output instruction whose address is /17 (23 decimal).

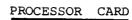

Interrupt must be used as follows (diagram 2.2.3.) :

- a Flag, outside the processor card, must memorize the interrupt request corresponding to each level and be reset by the corresponding recognition signal.

Reset takes place as soon as the interrupt is recognized.

#### II.3.2.2. Priorities :

The hierarchy of priorities at the processor's level is effective only at recognition and not at execution. It means that in case several interrupt levels show up together or are present together after unmasking, the one that will be recognized is the one holding the highest priority, in the order 7, 6, 5, 4, 3, 2, 1, 0. If the first instruction of the interrupt program (which cannot be interrupted) is not a general masking "MAS", the program will be instantly interrupted by any of the recorder interrupt levels, even if their priority is lower to the one currently being executed.

If the first instruction is a mask (MAS, it is then possible to proceed with a dynamic servicing of the interrupt'priority through "individual enable" instruction (OUT/17).

#### II.3.2.3. Execution :

When an interrupt is requested, and assuming it is enabled and unmasked, the processor will recognize it.

If it is disenabled, it will be recognized only after arming has taken place and in the absence of masking. If masking takes place, it will be recognized when unmasking takes place if there is no nigher priority level request.

When an interruption has been carried out, the current instruction is executed even if it includes several cycles. Afterwards, the program is connected to an address of page O which depends on the level as shown on diagram below :

| Niveau | Adresse D | Adresse H |

|--------|-----------|-----------|

|        |           |           |

| 0      | 0         | /00       |

| 1      | 8         | /08       |

| 2      | 16        | /10       |

| 3      | 24        | /18       |

| 4      | 32        | /20       |

| 5      | 40        | /28       |

| 6      | 48        | /30       |

| 7      | 56        | /38       |

|     | MAS<br>JMP SV3           | INTERRUPT MASKING<br>JUMP TO SV3          |

|-----|--------------------------|-------------------------------------------|

| sv3 | XXX<br>XXX               | SAVEGARD PROGRAM                          |

|     | XXX<br>DMS<br>XXX        | INTERRUPT UN MASKING<br>INTERRUPT PROGRAM |

| rs3 | XXX<br>MAS<br>XXX<br>XXX | INTERRUPT MASKING<br>RESTITUTION PROGRAM  |

|     | XXX<br>REI               | RETURN WITH UN MASKING                    |

ORG/18

# Figure 2.24

#### Examples of interrupt program :

Let's assume that level 3 interrupt program is to be written.

When an interrupt takes place, the program will be connected to instruction /18 (24 decimal).

Diagram 2.24 shows the program which will have to be used. In this program, interrupt have been masked during the safeguarding and program restitution (respectively SV3 and RS3). During the interrupt program, interruption mask has not been modified and the program can be interrupted by all the enabled interrupt levels, whatever their priority may be.

Note that a jump instruction is used almost immediately to avoid overlapping into the level 4 interrupt program starting at address /20.

> DIAGRAM 2.25 ORG 24 MAS LAI / O2 OUT 23 DMS JMP IT3 IT 3 ------

In that example, prior to entering the interrupt program itself, interrupt level 2 is disenabled and the "watch-dog" is switched-on. As soon as DMS instruction is executed, the program can be

interrupted by the interrupt levels 2 and 0 exclusively.

Note that the program starting at address /18 precisely contains 8 instructions.

Two more complete interrupt examples will be covered in the chapter related to the use of the channel stack.

II.3.3. Use of the real-time clock :

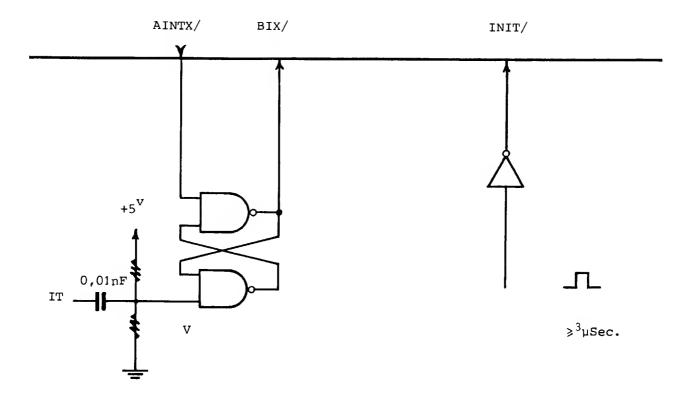

Real-time clock yields impulsions at a frequency determined by the time constant composed of a capacitor and infinite resolution multi-turn potentiometer.

Diagram 2.26 indicates the value of the capacitor to be used to obtain a desired range of frequency. The temperature stability of the capacitor is in direct relation with the clock's.

The potentiometer allows fine adjustment of the frequency within a 10/1 ratio.

The scale capacitor and the adjustment potentiometer are arrowed on stet. The four other potentiometers must remain untouched by the user. They are used for time base adjustment at the factory.

In the standard version, the internal clock is supplied at 10 milliseconds. Real-time clock can be connected on level 7 interrupt. This is obtained by wiring points A and B of the processor card (see photo 2.1). The processor card is supplied with this connection wired (except when MICRAL is delivered in a system where real time clock must not be used on interrupt). It is not necessary to connect the recognition output, as it is connected automatically on the card.

To disconnect the clock, simply disconnect A and B. It is important to note that the clock is triggable. It means that the first pulse following unmasking or enabling of level 7 is positioned at its nominal value.

## II.4. Technical specifications of the processing card

#### II.4.1. Consumptions :

. Typical values :

| 5 | V | : | 650 | mA |

|---|---|---|-----|----|

| 9 | v | : | 27  | mA |

#### II.4.2. Maximum loads on outputs :

| . Group 1 | : | A INT O/ to A INT/ 1/                               |

|-----------|---|-----------------------------------------------------|

| • Group 2 | : | I / I / SYNC                                        |

|           |   | $T_1 / T_2 / T_3 / T_3'$ / WAIT STOP                |

|           |   | RGZ 1/ - Clock output /                             |

|           |   | SO/ to SO <sub>13</sub> / / DO/ to D <sub>2</sub> / |

|           |   |                                                     |

Group 1 outputs have a single 74 series TTL input.

Group 2 outputs have a 74L series input for each connector, equal to a maximum of 22 TTL 74L inputs.

## Output specifications :

- . Group 3 : BI/1 to B17/

- . Group 4 : READY / READY C/

INIT/

MDO/ to MD7/

Group 3 inputs are similar to a 74 series TTL input.

Group 4 inputs have a resistance of 470 Ohm connected to 5 V.

As a consequence, they accept 74 series TTL circuits with anopen collector.

## Delay specifications :

READY : to avoid the processor entering a wait state, READY signal must return to zero at the latest 500 nanoseconds after the higher address has been delivered by the processor.

DATA : data must be given during T'3 state.

## III - Memory cards

#### III.1. Memory description :

MICRAL's memory is divided into 64 pages of 256 bytes. Its construction is based on a modularity which allows increases page by page for the mixed RAM memory and 4 by 4 pages.

To achieve that, memories are composed of integrated circuits laid out on the memory cards through supports. Each card contains a selecter circuit enabling the processor to identify and choose it. The address is delivered through SO/ to S13/ stet, card address through S11/ to S13/, page within the card through S8/ to S10/ and Byte within the page through S0/ to S7/.

The data is received through DO/ to D7/ and supplied to MDO/ to MD7. Terminals CCO and CCl indicate the type of cycle requested by the processor. CCO = O indicates a read cycle - CCl = O Fetch; CCl = data Fetch.

CCO = 1 CCl = 1 indicates a write cycle, CCO = 1 CCO = 0 indicates that the memory is not addressed.

As far as timings are concerned, the eight lower order bits address are delivered to the pluribus at T, CCO and CCl and the six higher order bits address at  $T_2$ . Data is exchanged at  $T'_3$ .

The memory cards can be supplied blank or filled. It is in the user's interest to order fitted cards, because they will be fully tested in accordance with MICRAL's specifications.

There are two types of memory cards namely :

- . the mixed memory cards;

- . the RAM memory cards.

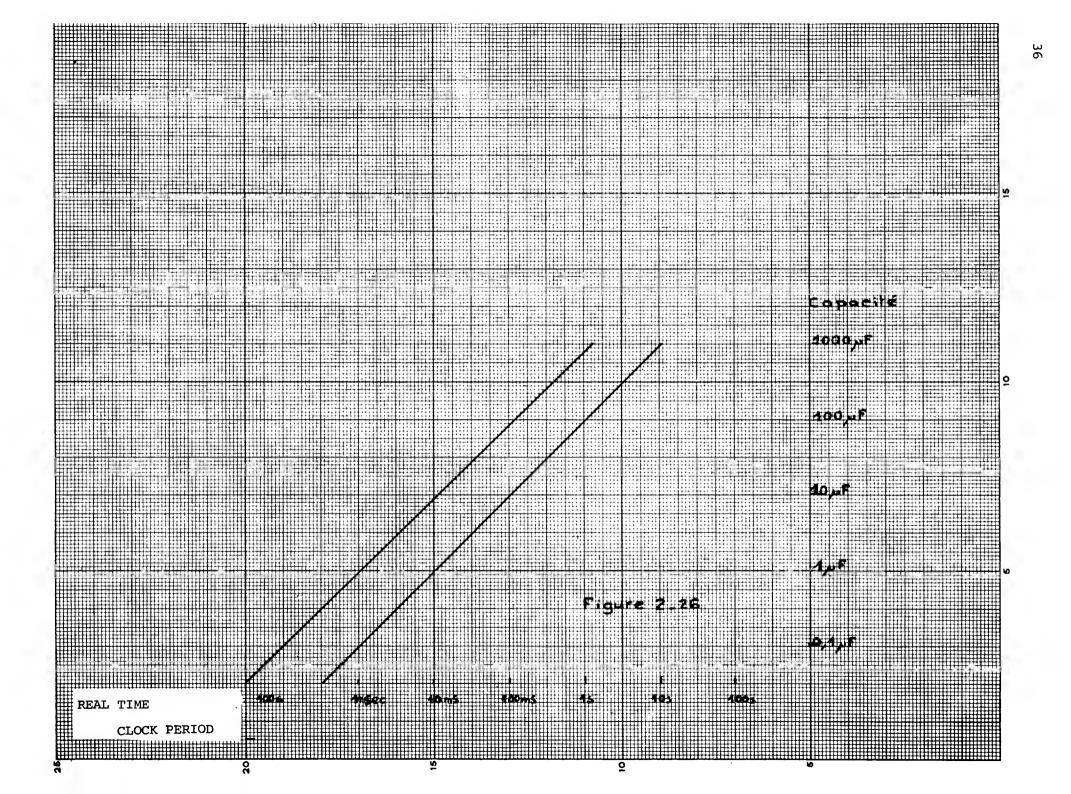

#### III.2. MI200 mixed memory cards

The mixed memory card, like the RAM, can contain up to 8 pages. The first seven pages are Read only memories (ROM). The eighth page can be either a Random access page (RAM) or a ROM page. This is done by inserting the desired circuits in the proper supports. The ROM circuits must be 1302, 1602 A or 1702 A circuits, respectively,

Total number of devices assigned : 8 pages or 2 K Bytes

Page seven may be ram or rom depending on circuits incering into the supports

Figure 3.1 - Mixed memory address assignation

depending upon whether a ROM is desired (see paragraph 1-2 of introduction), a PROM or a REPROM. These circuits are organized with 256 bytes which therefore constitute the minimal ROM increment.

The RAM page is composed of eight 1101 or 4007 circuits. These circuits are, 256, one bit, Static memories. One circuit assigns the eight pages addresses; the latest page of the card can be either a RAM or a ROM. Photograph 3.1 shows the mixed memory card. Diagram 3.1 defines the assignment of the memories (see complete clarification in paragraph 1.5).

#### III.3. M1202 Random memory card (RAM)

The RAM memory card can contain up to 2048 bytes, made of 1024, one bit, static memories. The complete card represents 8 memory pages.

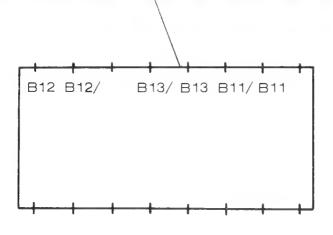

The assignment of the card address is achieved by a selecter circuit (photo 3.2.) which must be wired as indicated on diagram 3.2.Diagram 3.2. shows the memory card and the geographical location of the words within that page (see complete clarification in paragraph 1.5.).

A voltage protecter option is provided on MICRAL. It is made of a battery coming in through terminal "Protected supply" (A 5 on the pluribus). When the + 5 V disappears, the protected supply voltage maintains a level enabling the information to be held within the RAM. As soon as the + 5 V reappears, the data can be reutilized. While the 5 V supply disappears, it is not possible to read nor to write into the memory.

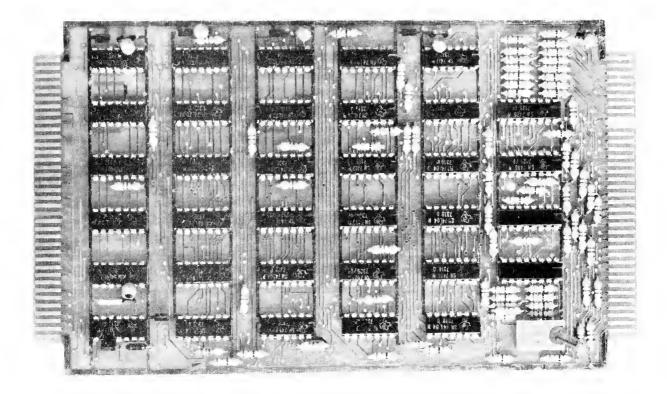

PHOTO 3.2

2K BYTES RAM CARD

ASSIGNED DEVICES

RAM

NUMBER OF DEVICES ASSIGNED : 8 pages or 2K Bytes

Figure 3.2 2K RAM CARD ADDRESS ASSIGNATION

IV - Coupling cards

#### IV.1. Direct interfaces - Specialized interfaces

MICRAL's outside coupling is done through inputoutput interfaces or through the stock channel.

Two types of interfaces are provided :

- . Direct interfaces connected to the pluribus;

- . Specialized interfaces connected to direct interfaces.

## IV.1.1. Direct interfaces

All the direct interfaces are connected in negative logic. It means that a one in the accumulator, when transferred into an output, will yield a low level. Likewise, when in an input, a low level will yield one in the accumulator.

Regarding the instructions, each input and each output will generate a signal. This signal indicates that the input data has been taken over or that the output data has been memorized. The direct interfaces are controlled by 8, i.e. by channel, which will be called byte input or output, having 8 wires. The expressions input and output are reserved to a "one wire" input or output.

Electrically, the interfaces are connected as follows : with the MICRAL to the pluribus (terminals DO/ to DO7/ for outputs and MDO/ to MD7/ for inputs), and with the peripheral by means of a connector which is supplied with the card.

#### IV.1.2. Specialized interfaces

They are connected in negative logic to the calculator. With the peripherals, they are obviously adapted to the specified levels. Generally speaking, they pick the power supply exclusively from the pluribus. The input and output signals are connected at the end of the direct interface cards.

#### IV.2. Inputs and outputs capacity

In MICRAL, 8 groups of input and 24 output bytes can be addressed directly. One of them, the 23, is used for enabling the interrupt levels. Each input and each output include eight wires. Besides, in MICRAL subaddressing of the inputs is obtained by precharging the accumulator. This allows addressing of up to 7 times 256 inputs of 8 wires.(At least, one group address is supposed to be used for a stack channel). Various interface cards allow these channels to be used.

#### IV.2.1. Addressing of inputs/outputs

At input, the group's address is on bits S9/, S10/ and S11/ of the pluribus, the channels address on bits S0/ to S7/ (S12/ and S13/ are of necessity OO).

At output, the address is on bits S9/, S10/, S11/, S12/ and S13/. The pattern S12 = 0, S13 = 0 is not used, being reserved for inputs.

Each interface has one or several selection circuits to assign the address of its channels.

The principle of interface assignment is as follows :

- for inputs, circuits are used to assign group and channel. This is done with jumpers on a support as with memories. For ease of identification, we shall designate group bits by BG and channel bits by BE.

- for outputs, a single circuit allows address assignment.

Exterior connections are at the end of the card, as shown on the board in diagram 4.3. An AC/ signal indicates that the input has been recognized or that the output has been memorized. Negative logic is used in both inputs and outputs.

#### IV.2.2. Exchange of data :

All the data goes through the accumulator. At input, two instructions are to be used in order to take full advantage of the system's capacity. The first instruction precharges the accumulator with the channel address, the second is the input instruction itself (including the group address).

LAI 215 Precharge accumulator

INP 2 Instruct input.

#### Diagram 4.1.

The two instructions on diagram 4.1 address channel 215 of Group 2. The eight bits of this input are transferred at T'3 in the accumulator, through bits  $MD_0$  to  $MD_7$  of the pluribus.

Output is different. One instruction executes the transfer of the accumulator's content to the eight bits of the channel, through bits  $S_0/$  to  $S_7/$ .

| Assigned devices           | BE<br>BS | Input couplers<br>Output couplers             |

|----------------------------|----------|-----------------------------------------------|

| Number of devices assigned |          | 4 bytes or 32 inputs<br>4 bytes or 32 outputs |

Figure 4.2 - 32 INPUTS 32 OUTPUTS ADDRESS ASSIGNED

45

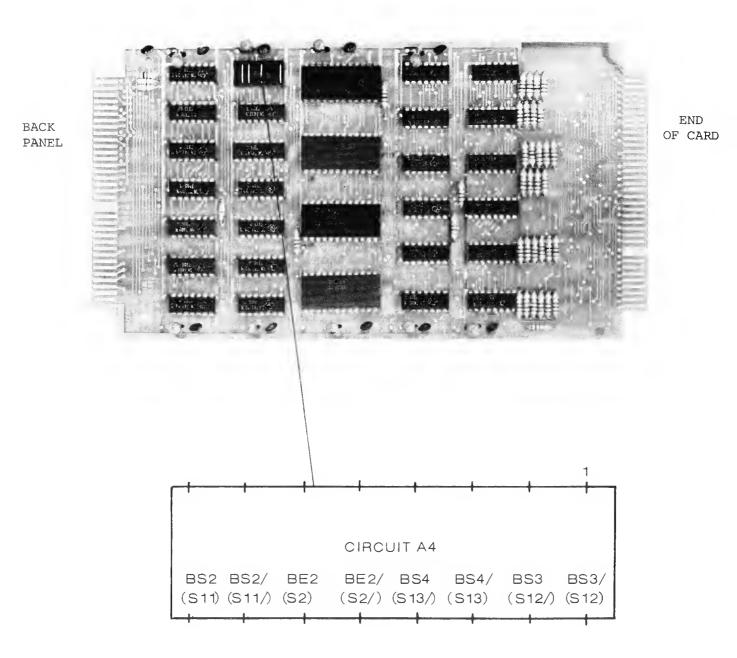

#### IV.3. M1400 32 inputs 32 outputs interface

This card connects 4 input bytes (32 inputs) and 4 output bytes (32 outputs). MICRAL system cannot receive more than 2 cards of this type. On input, they can be used only on group O's address. Therefore, it is not advisable to use this address as a stack channel. For input addresses, two configurations are possible. This is done by means of one single jumper which assigns 2 bits or the address register. Those two configurations are, respectively, channels 0, 1, 2, 3 and channels 4, 5, 6, 7.

For outputs, all configurations are acceptable except configuration 0-0 on the two highest bits, since this configuration is reserved to inputs. Diagram 4.2 shows the address assignments scheme on this card. BE for input bits and BS for output bits, have been used.

Exterior connections are performed at the end of the card, as shown on board in diagram 4.3.

An AC/Receipt signal indicates that the input has been recognized or that the input has been memorized. Negative logic is used for both inputs and outputs.

|       | <sup>B</sup> 7 | <sup>B</sup> 6 | <sup>в</sup> 5 | <sup>B</sup> 4 | в3         | <sup>B</sup> 2 | в <sub>1</sub> | в <sub>о</sub> | AC/         |

|-------|----------------|----------------|----------------|----------------|------------|----------------|----------------|----------------|-------------|

| ЕO    | A28            | A29            | <b>A</b> 30    | A31            | A32        | A33            | A34            | A35            | A36         |

| E1    | A19            | A20            | A21            | A22            | A23        | A24            | A25            | A26            | A27         |

| E2    | A10            | A11            | A12            | A13            | A14        | A15            | A16            | A17            | A18         |

| E3    | A1             | A2             | A3             | A4             | <b>A</b> 5 | A6             | А7             | A8             | А9          |

| s0    | в1             | в2             | в3             | в4             | в5         | в6             | в7             | в8             | в9          |

| SI    | в10            | в11            | в12            | в13            | B14        | в15            | в16            | в17            | в18         |

| 52 S2 | B19            | в20            | B21            | в22            | в23        | в24            | в25            | B26            | B2 <b>7</b> |

| S3    | в28            | в29            | в30            | в31            | в32        | в33            | в34            | в35            | в36         |

Interrupt input : B37 Ground A37

Example = Bit 4 of input 3 must be connected at A4

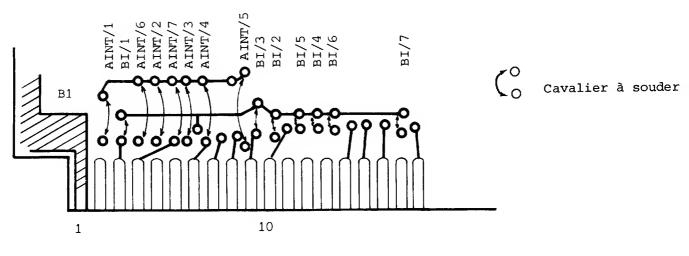

## INTERRUPT CONNECTIONS

BI/ = Bit d'interruption AINT/ = Annulation d'interruption.

Diagram 4.3. Interconnection sketch of the card 32 inputs 32 outputs

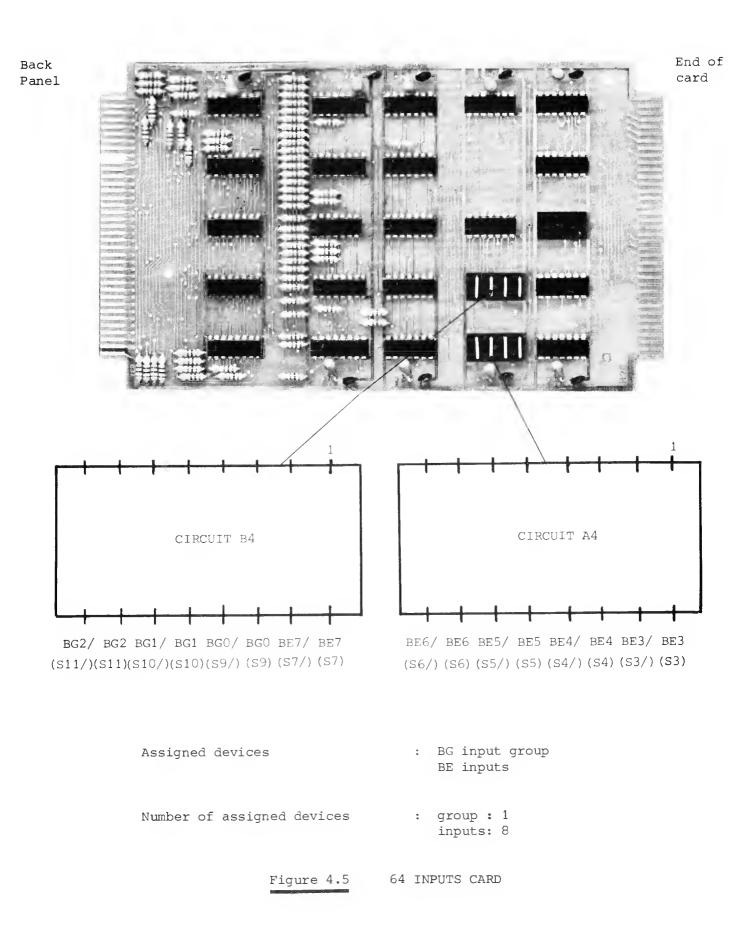

#### IV.4. M1401 64 inputs interface

This interface allows a tie up with eight input bytes. Photograph 4.2. shows this card with its three address assignment circuits.

Circuit 1 assigns the group addressed by the INP instruction.

Circuits 2 and 3 assign the address of the channel designated by the accumulator content. Circuit 3 defines the two highest order bits, circuit 2 the three lower one (Diagram 4.4.).

Input of interfaces to the peripherals is done at end of the card, as per interconnection scheme shown on diagram 4.5.

|                | AC/ | в7          | в6  | в5          | в4  | в3  | в2  | в1  | в0  |

|----------------|-----|-------------|-----|-------------|-----|-----|-----|-----|-----|

| е <sub>О</sub> | А9  | А8          | A7  | A6          | A5  | A4  | A3  | A2  | A1  |

| E <sub>1</sub> | в9  | в8          | в7  | в6          | в5  | в4  | в3  | в2  | в1  |

| E <sub>2</sub> | A18 | A17         | A16 | <b>A1</b> 5 | A14 | A13 | A12 | A11 | A10 |

| E <sub>3</sub> | в18 | в17         | в16 | <b>B1</b> 5 | в14 | в13 | в12 | B11 | в10 |

| E4             | A27 | <b>A</b> 26 | A25 | A24         | A23 | A22 | A21 | A20 | A19 |

| E5             | в27 | в27         | в25 | в24         | в23 | в22 | B21 | в20 | в19 |

| <sup>E</sup> 6 | A36 | A35         | A34 | A33         | A32 | A31 | A30 | A29 | A28 |

| E <sub>7</sub> | в3б | в35         | в34 | в33         | в32 | в31 | в30 | в29 | в28 |

## Diagram 4.5 - 64 inputs INTERCONNEXION DIAGRAM

Figure 4.6 - 64 OUTPUTS ASSIGNMENT

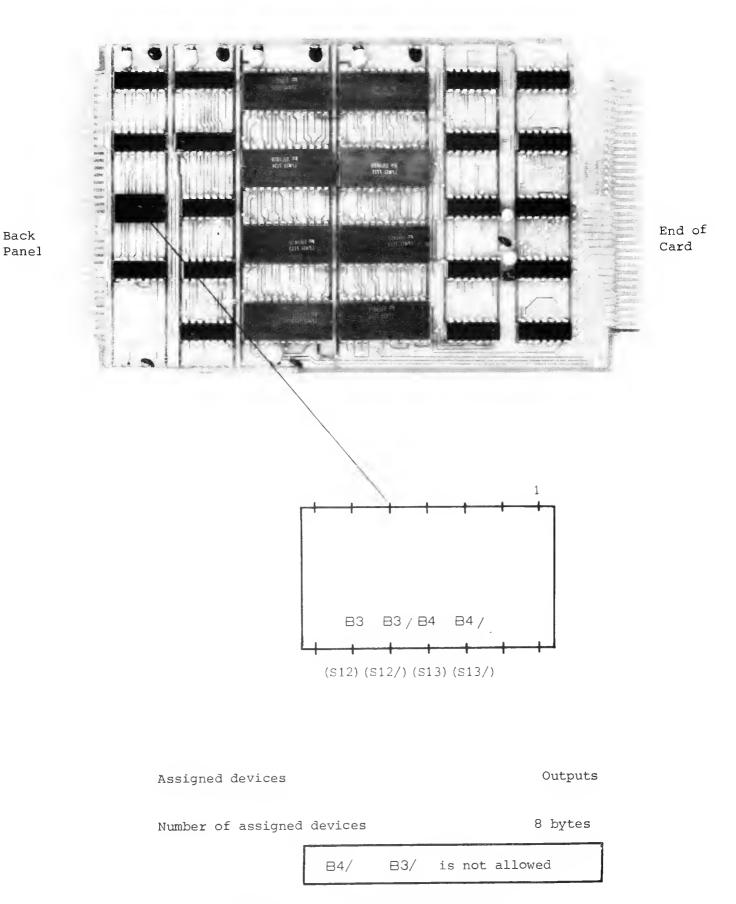

#### IV.5. M1402 64 outputs interface

It allows a tie up with 8"byte" outputs.

One single circuit allows address assignment since the maximal output capacity is 24 (Diagram 4.6.).

Care must be taken in output card address assignement to avoid OO configuration on bits 4 and 5 (reserved for inputs).

As a matter of fact, any output card wired on basis of this configuration could not be recognized by the processor. Output of the interfaces on the peripheral side is performed at the end of the card. The interconnection layout is defined on diagram 4.7.

|                | AC/         | B <sub>7</sub> | <sup>B</sup> 6 | в5          | в4  | B3  | <sup>B</sup> 2 | в1   | <sup>в</sup> о |

|----------------|-------------|----------------|----------------|-------------|-----|-----|----------------|------|----------------|

| s <sub>0</sub> | А9          | A8             | А7             | <b>A</b> 6  | A5  | A4  | <b>A</b> 3     | A2   | A1             |

| s <sub>1</sub> | в9          | в8             | в7             | в6          | в5  | в4  | в3             | в2   | в1             |

| s <sub>2</sub> | A18         | A17            | A16            | <b>A</b> 15 | A14 | A13 | <b>A</b> 12    | A11  | A10            |

| s <sub>3</sub> | в18         | в17            | в16            | в15         | в14 | в13 | в12            | в11  | в10            |

| s <sub>4</sub> | A27         | A26            | <b>A</b> 25    | A24         | A23 | A22 | A21            | A20  | A19            |

| s <sub>5</sub> | в27         | в26            | в25            | В24         | в23 | в22 | в21            | в20. | в19            |

| <sup>s</sup> 6 | <b>A</b> 36 | <b>A</b> 35    | A34            | <b>A</b> 33 | A32 | A31 | A30            | A29  | A28            |

| s <sub>7</sub> | в36         | в35            | в34            | в33         | в32 | в31 | в30            | в29  | в28            |

Figure 4.7 - 64 OUTPUTS CARD INTERCONNEXIONS

SWITCH

# Figure 4.8

JUMPER POSITION TO OBTAIN A DESIRED :

a) RATE

b) NUMBER OF CARACTER BITS

c) CONTROL MODE

(COMMON TO TTY AND MODEM)

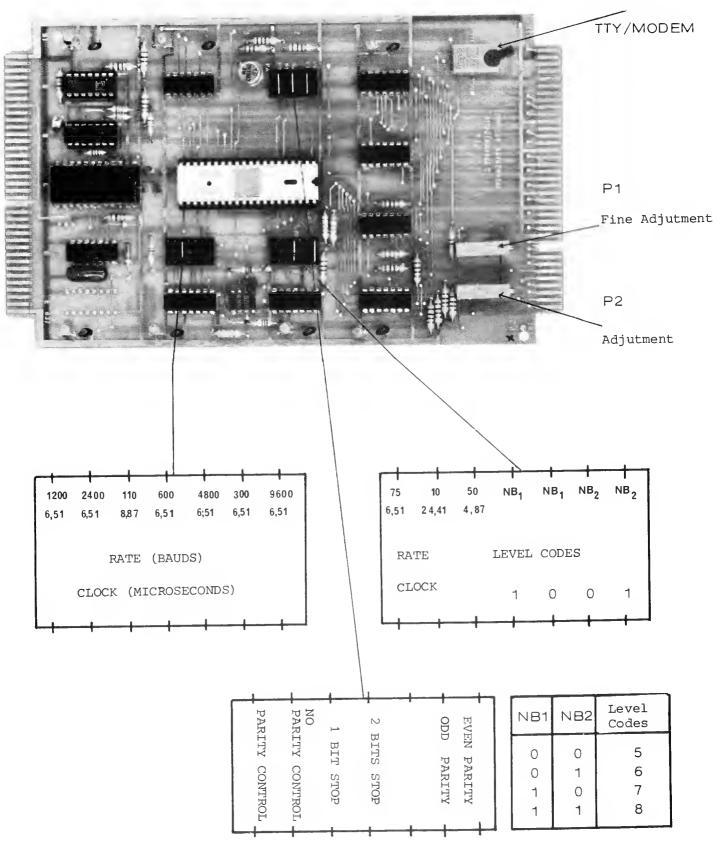

#### IV.6. Universal asynchronous interface TTY

IV.6.1. Description :

This is a specialized interface. It only works from the pluribus power supply voltages. Several input/output interfaces are required to control and exchange data. The card controls either a teletype, or a MODEM.

The cards include the circuits enabling adjustment to the rate of transmission. This is obtained through a clock placed inside the card. Its rate is adjustable by means of two potentiometers P2 and P1 and suitable counters. P2 controls rough adjustment and P1 fine adjustment.

Circuits similar to those used for address assignment allow the selection pre-adjusted rates and to operate using different types.

#### IV.6.2. Standard output rates :

To adapt the circuit to a desired rate, two adjustments are necessary.

- 1°) Adjust the clock's period by means of Pl and P2 potentiometers and regulate the frequencies.

- 2°) Select the counters by a jumper.

Diagram 4.8 clearly indicates the jumper's position and the clock period for each of the standard values : 0 - 50 - 75 - 110 - 300 - 600 - 1200 - 2400 - 4800 - 9600 Bauds.

IV.6.3. Types :

IV.6.3.1.Number of Movements :

These can be chosen between 5, 6, 7 and 8 by using two jumpers as shown on the chart.

#### IV.6.3.2. Parity control :

Two jumpers allow, one to carry out parity control, the other to perform it on even or odd parity.

#### IV.6.3.3. Stop bits :

Finally, one last jumper allows to accept one or two STOP bits.

Diagram 4.9. gives the interconnection of the functions.

| CONTROLS<br>VE/<br>AS/<br>PE/<br>PS/<br>SP/<br>ES/<br>EP/<br>GROUND | INPUT STROBE B9<br>OUTPUT STROBE B37<br>INPUT READY A29<br>OUTPUT READY A6<br>FRAMING ERROR A2<br>STOP BIT ERROR A16<br>PARITY ERROR A12<br>B11-<br>B21-<br>A36- |                         |                                             | -23                             | 5-17-19- |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------|---------------------------------|----------|--|

| DATA                                                                |                                                                                                                                                                  |                         |                                             |                                 |          |  |

| INPUT B1                                                            | B6/ B5/ H<br>B2 B3 H<br>A1 A13 A                                                                                                                                 | в4 в5                   | в6                                          | в7                              |          |  |

| Figure 4.10 In                                                      | terconnexions                                                                                                                                                    | common to               | TTY and                                     | a mode                          | М        |  |

| CONNEX<br>MOLEX CONNECTOR<br>5<br>6                                 | 5 B30                                                                                                                                                            |                         |                                             |                                 |          |  |

| 7<br>8                                                              |                                                                                                                                                                  | B27<br>B28<br>B29       |                                             |                                 |          |  |

| CLOCK AJUSTMENT<br>RATE JUMPER<br>LEVEL<br>STOP BITS<br>PARITY      |                                                                                                                                                                  | : 110 B<br>: 8 1        | MICROSEC<br>AUDS - 5<br>-14 and<br>ds on op | 5-10<br>4-11                    | D2       |  |

| Figure 4.11                                                         | ASR33                                                                                                                                                            | Interconn               | exion                                       |                                 |          |  |

| RQS/<br>RQS<br>DTR/<br>DTR<br>DSR/                                  | EMISSION REQU<br>TO MODEM<br>TERMINAL READ<br>TO MODEM<br>MODEM READY F                                                                                          | OY (From O<br>OR RECEPT | ION                                         | B22<br>B24<br>B25<br>B20<br>A34 |          |  |

| DSR<br>CTS/                                                         | (To input)<br>FROM MODEM B12<br>MODEM NOT READY FOR TRANSMIS-                                                                                                    |                         |                                             |                                 |          |  |

| CTS<br>CAR/<br>CAR                                                  | SION (To input) A21<br>FROM MODEM B14<br>CARIER NOT DETECTED (To input) A25<br>FROM MODEM B16                                                                    |                         |                                             |                                 |          |  |

| MODEM DA'<br>TDAT<br>RDAT                                           | MODEM DATA<br>AT TRANSMISSION TO MODEM B18                                                                                                                       |                         |                                             |                                 |          |  |

Figure 4.12 Modem Interconnexion

#### IV.6.4. TTY Mode description :

After the switch located on the card is positioned on TTY mode, the interface can be connected to a teletype. With a ASR 33 teletype, reader and punch control option must be used (the source current must 20 mA).

The connection is carried out on the connector board, which is on the back of the teletype, as per board in diagram 4.10. To accept the information outputed in parallel, a pulse must be sent on to the received data enable. This can be obtained simply by connecting it to the recognition signal of the output interface which has been used. When the information is accepted on an input, the input request must be acknowledged on the output recognition terminal.

The TTY, and MODEM, can be tested on the INPUT READY or OUTPUT READY terminal, in negative logic. Those signals can be used also for interrupt.

#### IV.6.5. MODEM Functioning :

Diagram 4.11 indicates input and output functions of the MODEM.

TDAT transmitted data to MODEM

- RQS emission request

- DTR data terminal ready

- RDAT data received from MODEM

- DSR MODEM ready to receive

- CTS MODEM not ready for transmission

- CAR Carrier not detected.

Input strobe, output strobe, input ready, output ready signals, as well as the three Error signals, must be used as with type TTY.

#### IV.6.6. Error signals :

A framing error signal indicates either an emission or a reception request, while the previous INPUT data has not yet released to the peripherical, and the input or output are not ready.

A stop bit Error signal indicates that the number of STOP bits is not in accordance with the one that has been specified by using a specific jumper.

A parity ERROR signal indicates that parity is not the one specified by the corresponding jumper.

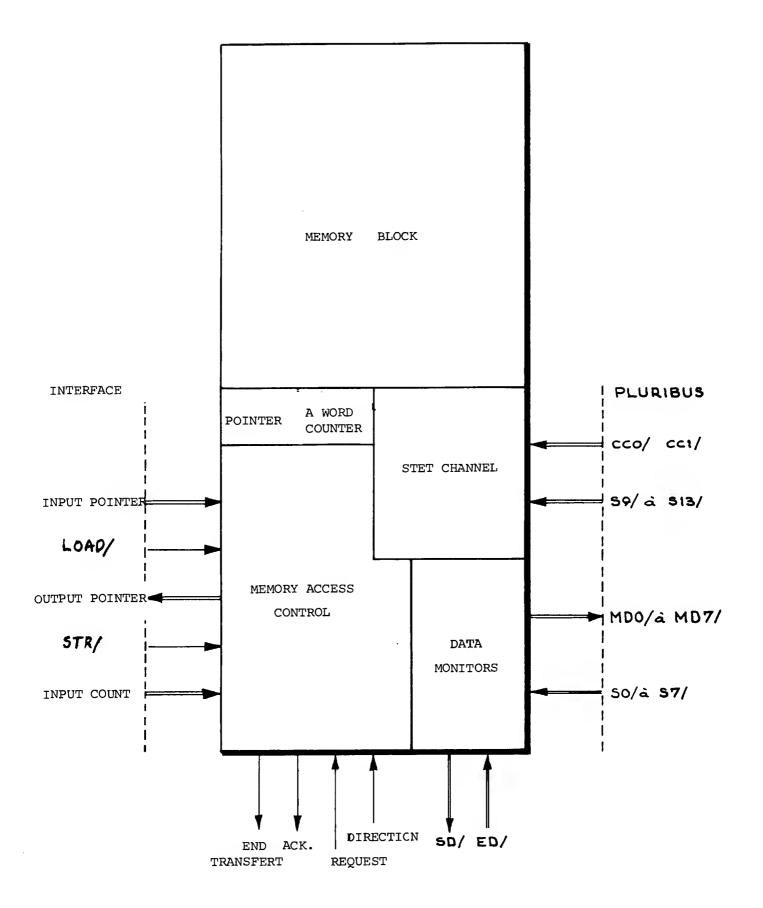

FIGURE 5.0 - CG CHANNEL STACK

#### PERIFERIK

Fig. 5.1. STACK CHANNEL

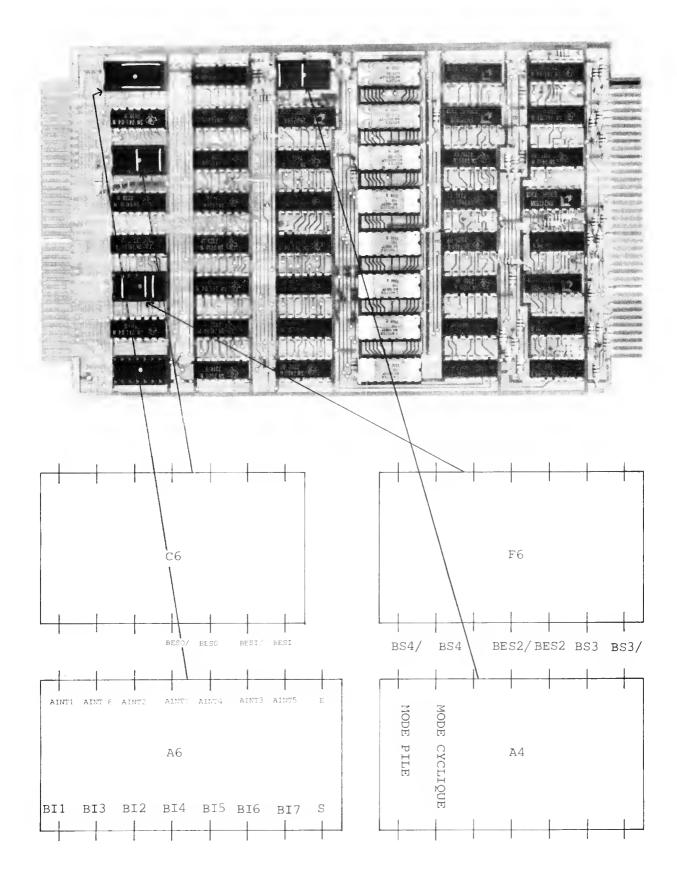

## V - Stack Channel Cards

V.1. General description of Stack Channel Cards (Diagram 5.1).

A stack channel card is made of a scratch pad memory with two multiplexed access :

- one to the processor is connected by terminals  $S_0/$  to  $S_7/$  in output and MD\_0/ to MD<sub>7</sub>/ in input.

- the other, to the exterior, is intended to connect a fast peripheral.

The latter is also composed of 8 bits in input and 8 bits in output.

The stack is composed of a random access memory addressed by a pointer updated automatically at each transfer of information. An input/output enables one, if desired, to read or write into the pointer register. They can be accessed through input and output interfaces. In the channel transfer mode, sequencing of the operations is performed by transfer request and receipt. An input controls the direction of the transfer. A word counter controls the performance by decreasing its content at each transfer and by stopping it automatically when the content is zero.

An input can precharge its content with a desired value. The channel transfer is initiated by loading the counter. The direction of the transfer can be controlled by the corresponding terminal. An OV signal on this output corresponds to "write" in the stack. A 5 V (or disconnected terminal) signal corresponds to "read" in the stack.

The end of the transfer, corresponding to zero on the word counter, generates an OV signal on the end of transfer output. This transfer can be utilized either through interrupt, or by test through an input interface. Upon input, only group addressing is used. It is therefore not necessary to precharge the accumulator to address the stack. This is done to increase access speed, but neutralizes the 256 inputs corresponding to the group address used.

In order to leave the possibility to utilize 32 input 32 output interfaces, which can only occupy group address 0, it is recommended not to use this address as a stack address.

| LAI | 25 | PRECHARGE WITH DESIRED ADDRESS |

|-----|----|--------------------------------|

| OUT | 15 | WRITE INTO POINTER             |

| ĹAI | 47 | PRECHARGE DATA                 |

| OUT | 6  | OUT PUT STACK                  |

# Figure 5.2

| LAI | 26 | PRECHARGE  | HIGHEST | BIT | ADDRESS |

|-----|----|------------|---------|-----|---------|

| OUT | 15 | WRITE INTO | POINTER | ٤   |         |

| INP | 6  | INPUT FROM | I STACK |     |         |

# Figure 5.3

| LAI | 127 | LOWEST BIT ADDRESS PRECHARGE  |

|-----|-----|-------------------------------|

| OUT | 15  |                               |

| LAI | 3   | HIGHEST BIT ADDRESS PRECHARGE |

| OUT | 16  |                               |

| LAI | 47  | DATA                          |

| OUT | 6   | OUTPUT TO STACK               |

# Figure 5.4

| ORG /10  |                   |

|----------|-------------------|

| MAS      | INTERRUPTS        |

| OUT STAK | A IN STACK        |

| LAB      |                   |

| OUT STAK | B IN STACK        |

| LAC      |                   |

| OUT STAK | C IN STACK        |

| LAD      |                   |

| OUT STAK | D IN STACK        |

| LAE      |                   |

| OUT STAK | E IN STACK        |

| LAH      |                   |

| OUT STAK | H IN STACK        |

| LAL      |                   |

| OUT STAK | L IN STACK        |

| DMS      | UNMASK INTERRUPTS |

|          |                   |

Figure 5.5

#### V.2. Functioning of the stack

## V.2.1. Stack utilization, through processor control :

Two instructions can progress into the stack by input or output addressed to the stack. INP STCK decrements the checker and then read the stack at the pointer's address. One remark here : when one reads the stack after the pointer has been located, it is not read at the loaded address, but one unit below.

OUT STCK writes into the stack and then increments the pointer. An OUT STCK will write in the same memory location as the read by a previous INP instruction, provided no modification of the pointer occurred between the two instructions.

## V.2.2. Access to the pointer and to the counter :

If access to the pointer is desired, it must be coupled through an input and an output interfaces. The accumulator must be precharged by the appropriate address : the desired address when a write instruction is to be done, the upper address when a read instruction is to be done.

An output instruction towards the corresponding interface's address then enables the transfer of the content of the accumulator into the pointer. One input or output instruction towards the stack then gives the desired reading or writing into the stack. Diagram 5.2. shows a set of instructions allowing to write 47 (taken as a data) at address 25 of the stack (assigned at address 6), the pointer being connected to interface 15. To read at the same address, the diagram's instructions should have been utilized.

Access to the counter is simpler : just transfer the precharged account in the accumulator towards the interface connected at the counter's input through an output instruction. This action activates the channel transfer process in the direction indicated by the corresponding order.

In the case of a 1024 byte stack, the pointer and the counter must be coupled throughout two byte inputs and two byte outputs.

For instance, the counter's loading instructions could look like diagram 5.3 (the counter's address for the high order bits being 15 and the counter's address for the low order bits being 16).

#### V.2.3. Utilization of the stack for saving register on interrupt :

Utilization of the stack is particularly interesting when an interrupt takes place. The registers and control indicators must be protected. The program counter in the processor's stack is protected by output instructions given to the stack address after a transfer in the accumulator by input instructions to the stack address. To avoid being interrupted while protecting the registers, MAS must be used as first instruction of an interrupt program. Since the first instruction after an interrupt cannot be interrupted, this safeguards the registers without the risk of being interrupted. Diagram 5.4. shows an example of a program safeguarding the registers corresponding to interrupt level 3. In that case, the control indicators are lost. If they have to be saved, they must be successively tested by conditional instructions without executing operations, increments and decrements to avoid modifying them.

#### V.2.4. Connection of a peripheral through the stack channel :

To connect a peripheral through a stack channel, a certain number of input/output interfaces must be provided for :

- 1°) one output to load the pointer;

- 2°) one input to read the pointer;

- 3°) one output to load the pointer;

The connections to the peripheral itself are the following :

- 1°) eight input wires of EDO/ to ED7/ data to be connected to the peripheral outputs;

- 2°) eight output wires of SDO/ to SD7/ data to be connected to the peripheral inputs;

- 3°) one input wire connected to the exchange request of the peripheral (DE/);

- 4°) one exchange receipt wire;

- 5°) one wire reporting the block transfer end FTB, which can be connected to an interrupt input as indicated in paragraph II.3.2.1.

Actually, it is possible to connect up to 10 peripherals to one single stack channel provided one is disposing of output interfaces designed to switch on the desired peripheral. In that case, only one peripheral will be active. The maximum of 10 is due to the FAN out of the circuits.

Control of the stack through the processor has priority on the automatic transfer mode. That means that each input or output directed to the stack address will set the counter to zero. To resume the transfer, the counter must be restarted.

#### V.2.5. Shape of signals :

Note that the connections to the pointer are optional and are necessary only if random access to the stack is desired.

The exchange request and receipt can be performed in two different ways :

- a) if the channel has been activated prior to any exchange request, the request may be a pulse less than 0,500 u.sec. wide.

Receipt then appears as a pulse of 0,6 microsecond coming at the latest 0,5 microsecond after exchange is requested;

- b) if the channel has not been activated, the request appears in the form of a level which is reset when the first discharge signal shows up. Negative logic is used. To load properly the pointer and the counter, they must be verified by means of the receipt output of the corresponding interface on LOAD/inputs for the pointer and STR/ for the counter.

CHANNEL STACK CONNEXIONS

| 1°) With other channels |     |

|-------------------------|-----|

| LINK IN                 | В11 |

| LINK OUT                | В2  |

2°) With peripherals

| DT/<br>BT/<br>STDO/<br>IN/OUT/ | Data out | Flip Flop | B17<br>B4<br>B3<br>A1 |  |  |

|--------------------------------|----------|-----------|-----------------------|--|--|

| CD/ (0 à                       | 7) Data  | output    | voir tableau          |  |  |

| CS/ (0 à                       | 7) Data  | input     | voir tableau          |  |  |

3°) Through input/output ports

| TC/<br>PA/ (0 à 7) | Cyclic transfer<br>Address precharge                          | A35<br>voir | tableau            |

|--------------------|---------------------------------------------------------------|-------------|--------------------|

|                    | Address strobe<br>Pointer address<br>Programmation long block |             | tableau<br>tableau |

| STPC/<br>BTB/      | Counter strobe<br>End of Block signal                         | A12<br>A10  | в10                |

4°) Ground

A36 et A37

|                  | В7  | в6  | в5  | в4  | в3  | в2  | в1  | в0  | Strobe |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| CD0/ à CD7/      | A30 | A31 | в27 | в22 | в12 | A11 | А9  | А8  | в3     |

| CS0/ à CS7/      | в6  | А5  | в8  | A6. | в7  | A7  | А3  | в5  | B17    |

| PAO/ à PA7/      | в30 | в31 | в32 | в33 | в34 | в35 | в36 | в37 | в29    |

| AO à <b>A</b> 7/ | A21 | A22 | A23 | A24 | A25 | A26 | A27 | A28 |        |

| PRO/ à PR7/      | A13 | A14 | A15 | A16 | A17 | A18 | A19 | A20 | A1 2   |

## FIGURE 5.7.

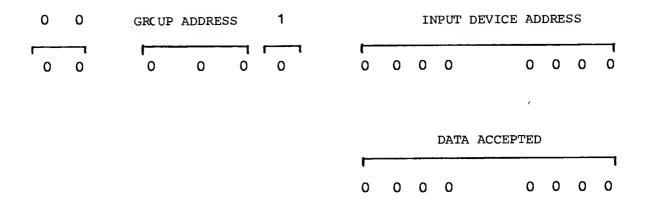

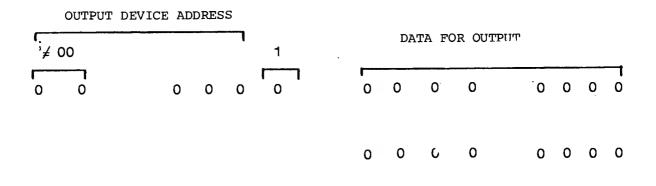

Figure 6.1 - EXPLANATION OF OP CYCLE LIGHTS

(FOR READ CYCLE SAME CONFIGURATION)

G T 17 .... 17 17 G ê () () U.U.U.U.LUD 0000 6 Ø 3 10-3

÷.

PHOTO 6.2 FRONT PANNEL REAR VIEW

PHOTO 6.3 CONSOL CARD

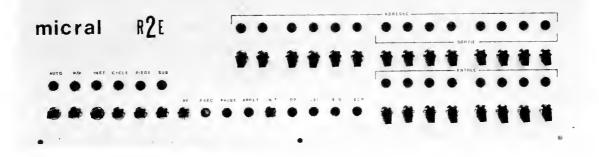

## VI - Visualization console

#### VI.1. General principles concerning visualization :

MICRAL's principal use is in process control. It does not aim to be an universal mini-computer. For this reason, the console is not supplied in the standard version.

Generally speaking, when MICRAL is utilized within a system, a console matching the particular application will have to be designed. The simpler it is, the easier it can be used by people who are not familiar with data processing. Just a signal, indicating a normal RUN, will be often sufficient. The optional console of MICRAL (photo 6.1) is actually meant for studies, adjustment, servicing and for systems handled by specialized personnel. The console enables them to command the mode with which MICRAL will work, as well as to visualize certain information needed for during use.

#### VI.2. Modes :

MICRAL, equipped with the console, can run under five modes :

- . automatic;

- . stepping;

- traps;

- Substitution;

- servicing.

#### VI.2.1. Automatic mode :

It is the normal mode of operation. In this mode, programing instructions proceed normally and can be stopped only by lack of low voltage on READY/terminal of the pluribus and by a HLT instruction. To get the automatic mode, depress fugitive key AUTO and at the same time make sure that signal TRAP is out. If it is lit, press on key TRAP to put it out.

RUN lightdisplay must be on WAIT and the stop light off, indicating that the program proceeds normally. If signal RUN goes off, one of the signals WAIT or STOP must keep alight indicating to the operator in what state the system is. In the WAIT state, it indicates that the program has presented a HLT instruction.

By examining the lights, whose sequence is determined by the processor, one can interpret those memory areas which are the most requested. In the STOP state, the lights marked address indicate which address the program has stopped at. The eight right hand lights display the lower order address, the six left hand display the higher address, which is the page address.

The eight lights marked INPUTS display the content of the addressed memory or the data supplied by an input interface. In the WAIT state, the cycle lights (FETCH READ I/O WRT) indicates the cause for the WAIT state : the memory is at fault when one of the lights is lit. A peripheral is at fault when I/O light is on. It is particularly the case when a wrong address is concerned. The meaning of the signal will be analyzed in the paragraph describing the stepping mode.

#### VI.2.2. Stepping mode :

To switch to stepping mode, depress fugitive "step" key. The RUN light goes out. The step light comes on. The stepping mode provides two options :

- instruction;

- cycle.

In the first one, the processor is set in WAIT state at each instruction on FETCH cycle. To get this option, depress fugitive key INS (the corresponding light comes on).

In the cycle option, the processor is set in WAIT state at each memory cycle.

In both cases, stepping is obtained by pushing STEP key. Clarification of the signals in WAIT state is given in following paragraphs and diagrams 6.1 - 6.2 - 6.3.

In the INS position, when at least one step is made, the ADDRESS lights display the instruction address to be executed at the next step and the INPUT lights display instructions to be executed, thus allowing the control execution of the program.

In the cycle position, interpretation of the lights depends upon the cycle lights :

- in OP, the meaning is the same as in previous paragraph;

- in READ or WRITE, the memory address can be read;

- in READ, the input signals display the data delivered to the processor by the memory;

- in I/O, the left hand bits of the address display the six lowest order bits of the instruction to be executed. The two highest order bits report that the instruction is an input when they are in OO pattern and that the instruction is an output when the pattern differs from OO.

On input instructions, the three following bits display the group address. The eight bits of the lower order address display the input address. The data to be noted is displayed on the input lights.

On output instructions, lowest order bits of the higher address indicate the peripheral's address. The eight bits of the lower address, marked OUTPUT, indicate the data to be exchanged.

To get out of the stepping mode, depress the desired mode key.

#### VI.2.3. Trap mode :

In the TRAP mode and in RUN, the program will proceed normally until the ADDRESS lights and the keys below these lights present the same pattern. When coincidence occurs, the processor goes automatically in stepping mode and a synchronization pulse is generated. Coincidence can occur only in OP cycle, thus enabling the program to be stopped at a desired FETCH address.

To switch to TRAP mode, depress the fugitive key (the corresponding light comes on).

After coincidence has occured, stepping can be performed by using step key. As soon as AUTO key is depressed, the processor will carry on normally until a new coincidence occurs.

To get out of TRAP mode, depress again TRAP Key. TRAP mode can be used in a different manner : by disconnecting the two points marked A and B on photograph 6.1 representing the console, the program does not stop any longer at the coincidence, but generates a pulse on the TEST terminal allowing the synchronization of an oscilloscope.

#### VI.2.4. Substitution mode :

In this mode, the configuration displayed by the INPUT marked keys is substituted to the memory output, enabling it to enter a program from the console, in stepping mode.

## VI.2.5. Repair mode :

In this mode, there are several possibilities :

1°) by means of a switch located on the console, an automatic substitution mode can be obtained in which the READY/terminal is automatically fed with a low voltage current to prevent WAIT state.

The instruction displayed by the keys is processed indefinitively so observation can be made easily;

2°) a switch placed in the back of the console (diagram 6.2.) prevents the execution of a zero instruction when the power supply starts up. In that case, the processor sets itself immediately in stepping mode, enabling, through substitution mode, to enter at any address of the program without executing the instruction of the address.

#### VI.3. Putting the console out of service :

This is effected by depressing the second switch at the back of the console (see photograph 6.2.).

## PHOTO VII.1 PLURIBUS

## VII - The pluribus

#### VII.1. General description :

The pluribus performs two functions :

1°) materially, supports the cards that perform the various functions;

2°) electrically, connects the cards one to another.

Electrically, the pluribus includes 74 terminals of which 9 are unused.

Annex 1 lists terminals with their functions.

Fuctions are broken down as follows :

- Power supplies

- . Control signals

- Addressing signals

- . Data

Clarification for each function is given in the description of the cards where they are generated and used.

A general descriptive paragraph is given in the technical appendix.

VII.2. Functional description of the terminal :

VII.2.1. Power supplies :

| Ground | A/ | A37 | Max. | Current |

|--------|----|-----|------|---------|

| + 5 V  | в/ | B37 |      | 1 A     |

| - 9 V  | B2 |     |      | 1 A     |

Memory protect voltage.

The emergency terminal enables the MICRAL to maintain a voltage on the RAMS so as to avoid losing information upon mains supply failure. It is not supplied in the standard version.

## VII.2.2. Synchronization :

All these signals are generated by the processor and utilized on all the other cards.

$\phi_{2}$  A8

It is the time base phase used to determine precisely all MICRAL's functions. From the processor a viewpoint, two  $\overline{\phi}_2$  can be used :

the first in phase with SYNC designated by  $\oint 21$ , the other in phase with SYNC designated by  $\oint 22$ .

SYNC/ B23

Defines the basic period of the processor.

$T_2 / - A27$

The signal relates to the addressing period of the highest order of the memory address, of the group address in the input instruction and of the address of the output peripheral.

T3/ - A35

Gives the state of the processor which immediately follows T2 state or WAIT state.

T'3 A28

Comes from the processor and is used in all the cards. This timing is the most important under the user's viewpoint. The MICRAL depends upon this timing to monitor information correctly. It must come up no later than 500 nanoseconds from the end of T2, and have covered T3.

If the data appears too late on the bus, there is a chance that the processor will take wrong information into account. To avoid this simply, do not apply READY/ until the data is established. Then, no risk of taking wrong information into account.

CCO/ A30

CC1 A31